Computers and Technology, 21.05.2020 22:16 smariedegray

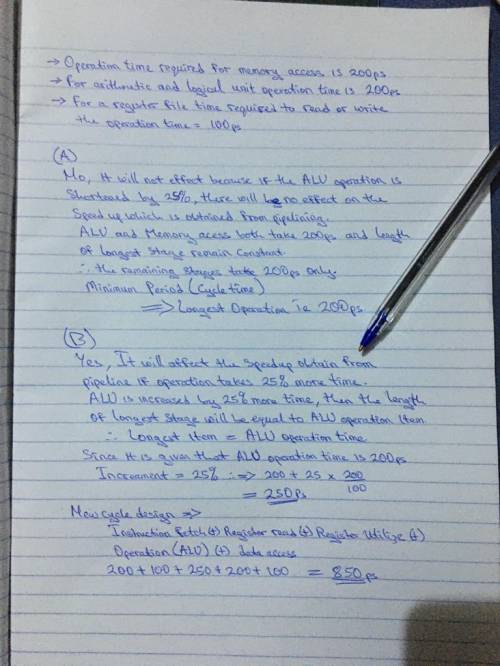

The operation times for the major functional units are 200ps for memory access, 200ps for ALU operation, and 100ps for register file read or write. For example, in single-cycle design, the time required for every instruction is 800ps due to lw instruction (instruction fetch, register read, ALU operation, data access, and register write). Here, we only consider lw instruction for speedup comparison. [2 pts]

a. If the time for an ALU operation can be shortened by 25%, will it affect the speedup obtained from pipelining? If yes, why? Otherwise, why?

b. What if the ALU operation now takes 25% more time? Will it affect the speedup obtained from pipelining? If yes, why? Otherwise, why? Then what is clock cycle time?

Answers: 1

Another question on Computers and Technology

Computers and Technology, 22.06.2019 10:40

5. illustrate how fine-line inventory classification can be used with product and market segments. what are the benefits and considerations when classifying inventory by product, market, and product/market?

Answers: 2

Computers and Technology, 22.06.2019 18:10

How can i delete permalinks from a word press site?

Answers: 1

Computers and Technology, 24.06.2019 15:30

What type of forensic evidence was recovered during the bomb set off at the new mexico facility on the video that was similar to the evidence obtained at the boston bombings and how did the evidence allow the researchers to connect other pieces of evidence to the same bomb?

Answers: 2

You know the right answer?

The operation times for the major functional units are 200ps for memory access, 200ps for ALU operat...

Questions

History, 30.08.2019 17:30

Chemistry, 30.08.2019 17:30

Mathematics, 30.08.2019 17:30

History, 30.08.2019 17:30

Physics, 30.08.2019 17:30

Mathematics, 30.08.2019 17:30

Chemistry, 30.08.2019 17:30

Mathematics, 30.08.2019 17:30

History, 30.08.2019 17:30

Biology, 30.08.2019 17:30

English, 30.08.2019 17:30

Computers and Technology, 30.08.2019 17:30

Computers and Technology, 30.08.2019 17:30

Arts, 30.08.2019 17:30